“选择性”科学家开发选择性原子沉积技术,提升集成电路自对准工艺制造效率与精度

今天,很高兴为大家分享来自DeepTech深科技的科学家开发选择性原子沉积技术,提升集成电路自对准工艺制造效率与精度,如果您对科学家开发选择性原子沉积技术,提升集成电路自对准工艺制造效率与精度感兴趣,请往下看。

来源:DeepTech深科技

随着技术的发展和市场需求,芯片制程逐渐往更小尺度发展,但芯片制造过程中,需要反复的沉积、光刻、刻蚀等繁琐步骤制约了其精度与可靠性。

图丨华中科技大学陈蓉教授团队选择性原子层沉积小组(来源:该团队)

图丨华中科技大学陈蓉教授团队选择性原子层沉积小组(来源:该团队)华中科技大学陈蓉教授团队自主研发了一种高精度薄膜沉积的解决方案。他们通过选择性原子层沉积技术(Selective Atomic layer deposition,ALD),实现了目标介电层在底部介电层的自对准生长,而在非生长区金属铜表面不生长。该工艺在生长区达到 5nm 厚度,非生长区不生长,其选择性达到 100%,并实现自对准沉积。

该技术对于领域的重要意义体现在,对于芯片先进制程来说,是非常重要的方法之一,其在对准精度、减少边缘对准误差、提升芯片制程良率等方面都具有优势。

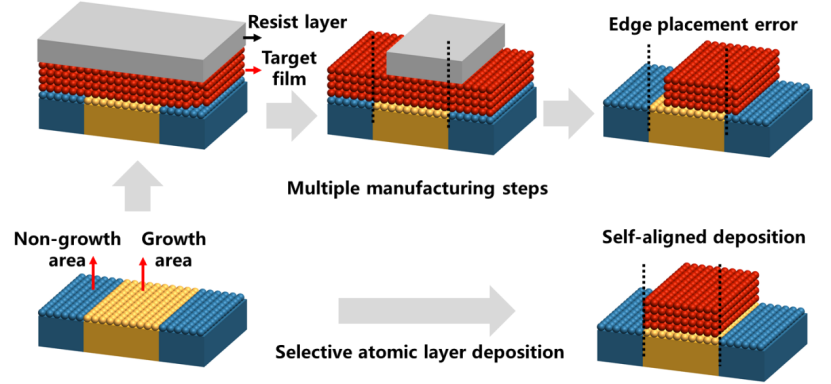

图丨在预定义的图案表面对准沉积图案化薄膜的两种技术路线,其中选择性沉积减少了再次光刻与材料刻蚀去除的复杂步骤且实现了高精度自对准 [1](来源:该团队)

图丨在预定义的图案表面对准沉积图案化薄膜的两种技术路线,其中选择性沉积减少了再次光刻与材料刻蚀去除的复杂步骤且实现了高精度自对准 [1](来源:该团队)在本次新研究之前,陈蓉教授课题组在该领域已进行了多年的技术累积。该课题组在领域内首次发表了关于固有选择性原子沉积技术综述,对该技术的近期发展进行了总结 [3]。

该研究是团队前期成果的延续,2022 年,该团队从研究机理上揭示了表面酸碱性、电负性等表面本征性质对选择性原子沉积的影响机制[4]。

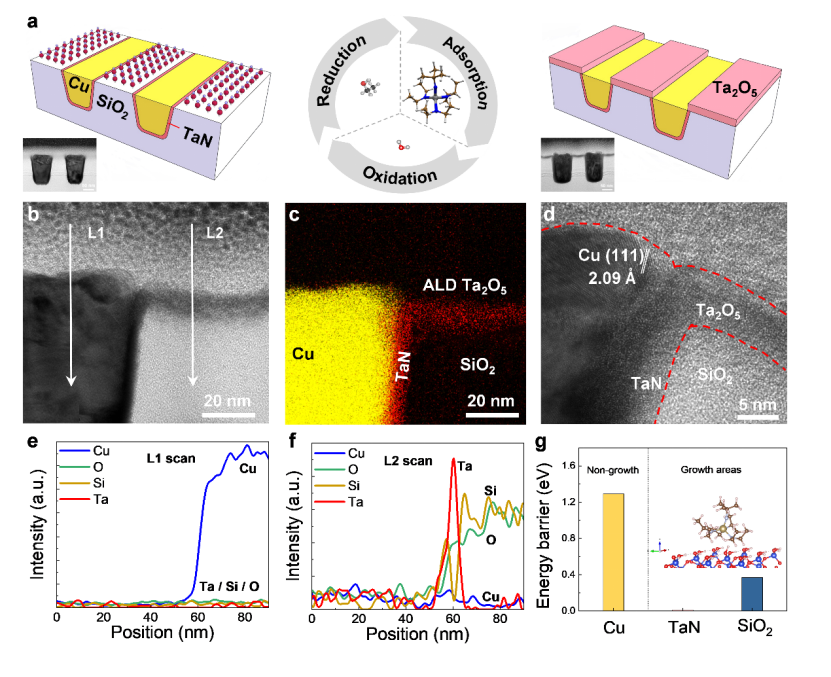

图丨在纳米图案化基底上实现了薄膜的自对准沉积(来源:Nature Communications)

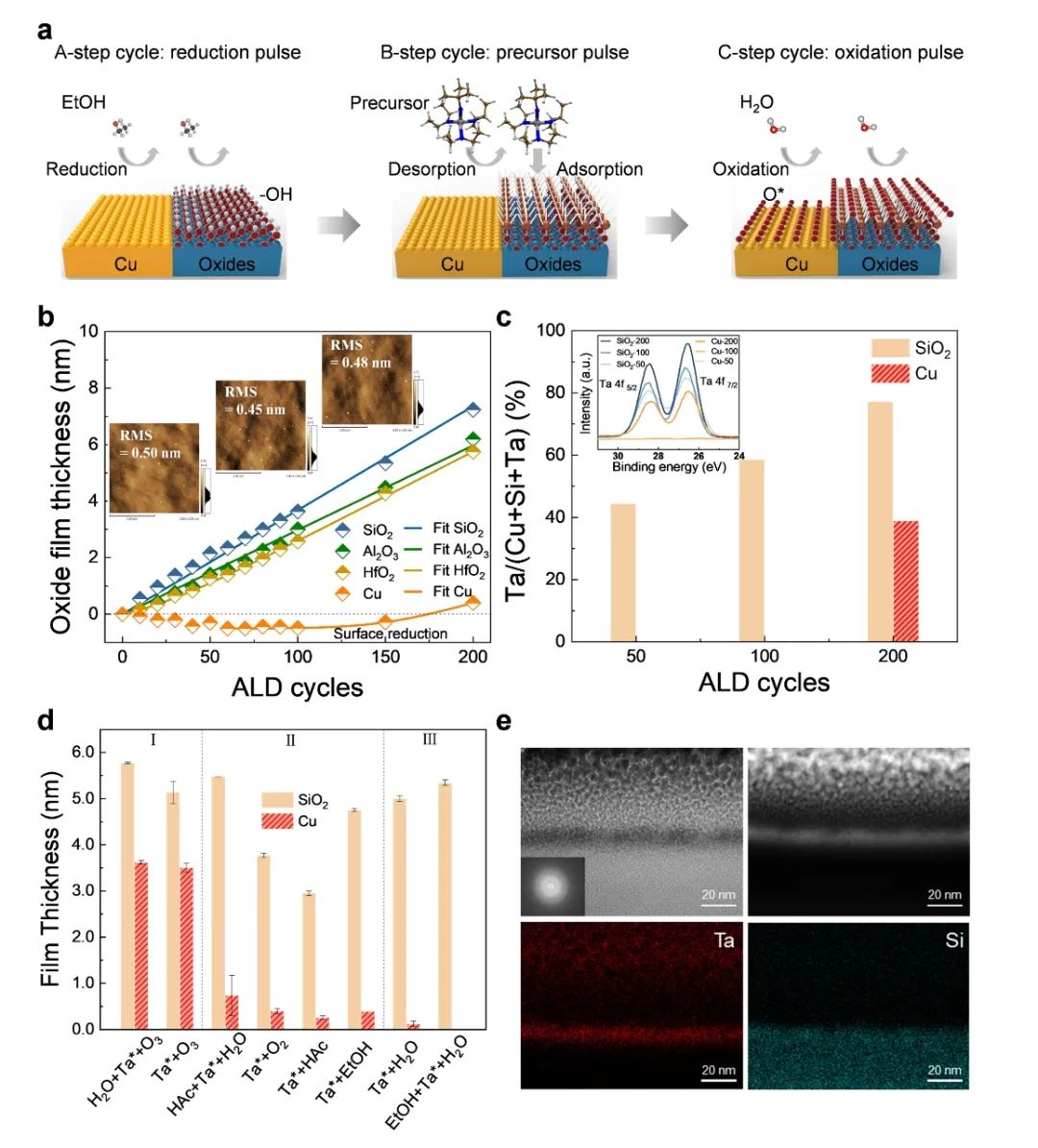

图丨在纳米图案化基底上实现了薄膜的自对准沉积(来源:Nature Communications)该研究发现铜表面不同氧化状态会造成非生长区表面形成缺陷位点,这些形核缺陷导致了选择性的丧失。研究团队突破了常规 ALD 两步循环交替生长,增加了原位还原修正步骤。

该团队提出的“循环耦合”工艺,使传统 AB 双循环转变为 ABC 多循环耦合,进而能够实现“表面原位还原-生长-缺陷去除”的步骤,有效抑制铜表面缺陷形核产生,最终实现高精度自对准。

图丨基于“循环耦合”的选择性原子沉积工艺(来源:Nature Communications)

图丨基于“循环耦合”的选择性原子沉积工艺(来源:Nature Communications)在原子沉积领域要想实现“选择性”,一般来说,需要在非生长区制备阻挡层。例如,引入自组装分子使其在非生长区钝化,阻挡原子层沉积生长,最后再将表面的阻挡层去掉[5,6]。而该研究发展的固有选择性,具有全气相工艺流程,且无需阻挡剂生长、去除等步骤,更加简洁与可靠。

该研究相当于开辟了一个新的方向,利用表面的差异,在不添加任何阻挡剂的条件下,靠前驱体的选择和工艺动力学调控实现了无模板、无阻挡剂的选择性生长,即通过本征的固有选择性实现了形核延迟和高选择性自对准沉积。

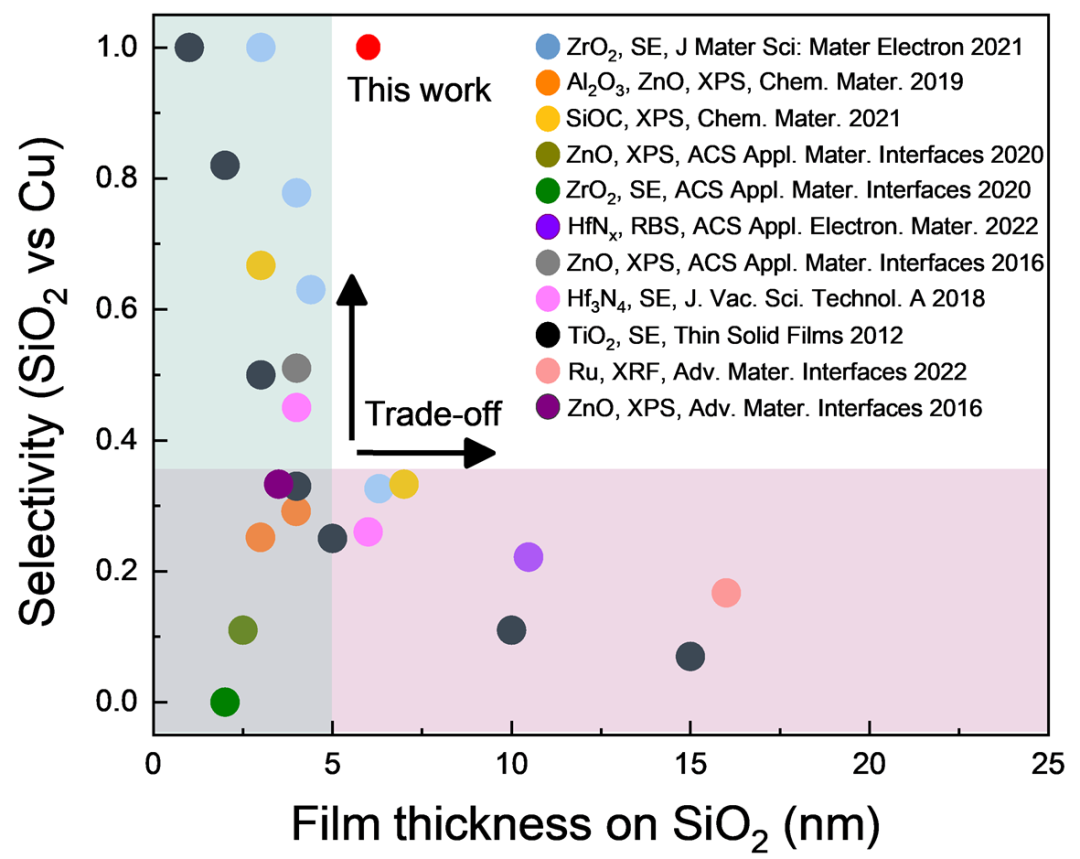

在该研究中,原子沉积技术工艺的自对准选择性接近 100%,生长区膜厚达到 5nm,非生长区完全无生长,达到固有选择性研究中所见报道最高值,这是在课题组多次尝试后的结果。

图丨固有选择性 ALD 方法在氧化硅与铜表面的选择性和膜厚度(来源:Nature Communications)

图丨固有选择性 ALD 方法在氧化硅与铜表面的选择性和膜厚度(来源:Nature Communications)一般来说,膜越厚选择性越差。在选择性沉积领域,选择性具有极限厚度,如果形核延迟太短,即使非生长区也会生长。而该研究中不仅实现了在生长区长出 5nm 厚度,而且在非生长区可以保持完全不生长,该现象在此前是从未有过的,这对于提升选择性沉积工艺可靠性至关重要。

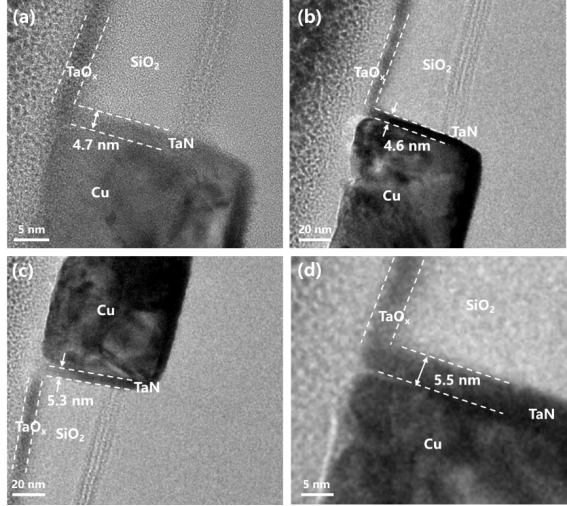

在芯片制程中,另一个很重要的问题是,生长的膜会出现“横向扩展”现象。也就是说,薄膜既往基底垂直方向生长,又会往两侧横向生长,导致它们会扩散扩展到铜区域从而降低工艺可靠性。

在该研究中,不仅实现了非生长区铜表面无生长,而且抑制住了生长区沉积薄膜的边缘扩展,薄膜生长停止到铜边缘。“这对于进一步提升对准精度,以及降低对准工艺后造成的金属电阻上升具有非常重要的作用。”该团队表示。

图丨选择性原子沉积薄膜横向扩展生长观察(来源:Nature Communications)

图丨选择性原子沉积薄膜横向扩展生长观察(来源:Nature Communications)下一步,他们将继续开发先进选择性 ALD 技术,扩展固有选择性方法到芯片各层对准工艺形成完整的工艺包。另一方面,他们计划继续开发小分子钝化、原位缺陷消除等全气相选择性沉积工艺。

为了将工艺在产线上验证,研究团队在国家重点研发计划颠覆性技术创新重点专项项目“面向芯片先进制程的选择性原子层沉积工艺与装备研发”支持下,也正在开发选择性沉积设备,以在芯片企业中进行流片试验。据悉,目前该团队已经与相关公司合作推进技术的产业化落地。

“我们计划明年实现选择性 ALD 工艺原理在生产线的初步验证,该工艺在国际上非常前沿,我们有信心在选择性原子沉积领域位列国际第一方阵。”该团队表示。

参考资料:

参考资料:1.https://protocolsmethods.springernature.com/posts/atoms-grow-where-desired

2. Li, Y., et al. Self-aligned patterning of tantalum oxide on Cu/SiO2 through redox-coupled inherently selective atomic layer deposition. Nature Communications 14, 4493 (2023). https://doi.org/10.1038/s41467-023-40249-2

3. Cao,K., et al. Inherently Selective Atomic Layer Deposition and Applications. Chemistry of Materials 2020, 32, 6, 2195–2207. https://doi.org/10.1021/acs.chemmater.9b04647

4.Li,Y., et al. Chemistry of Materials 2022, https://doi.org/10.1021/acs.chemmater.2c00851

5.Chen,R.,et al.Chemistry for Positive Pattern Transfer Using Area-Selective Atomic Layer Deposition. Advanced Materials(2006). https://doi.org/10.1002/adma.200502470

6.Liu,X., et al. Oxide-Nanotrap-Anchored Platinum Nanoparticles with High Activity and Sintering Resistance by Area-Selective Atomic Layer Deposition. Angew. Chem. Int. Ed. 2017, 56, 1648. https://doi.org/10.1002/anie.201611559

运营/排版:何晨龙

好了,关于科学家开发选择性原子沉积技术,提升集成电路自对准工艺制造效率与精度就讲到这。

版权及免责声明:凡本网所属版权作品,转载时须获得授权并注明来源“科技金融网”,违者本网将保留追究其相关法律责任的权力。凡转载文章,不代表本网观点和立场,如有侵权,请联系我们删除。

相关文章

- “西湖”西湖大学成立5周年,施一公:做创新的守护者是使命也是未来

- “儿子”妈妈将50余万“读书钱”存儿子名下,19岁儿子取出转给女友,妈妈无奈起诉追回

- “力学”王博已任大连理工大学副校长

- “说了”云朵的话语,心灵的方剂 ——读周实《有些话语好像云朵》

- “超新星”云南天文台发现Ia型超新星前身星候选体

- “科幻”和成都和教育,一起遇见未来!两份重要“科幻教育”名单公布

- “红星”梁静茹南京演唱会再现“柱子票” 主办方:临时布置追光灯,正与观众沟通

- “导盲犬”视障女子自曝带导盲犬进公园遭保安阻拦 公园方:天色较晚不知其实情,沟通后已放行

- “小行星”首次!我国计划实施近地小行星防御任务

- “肿瘤”科学家揭示肿瘤免疫逃逸新机制,鉴定三个癌症生存相关因子,为肿瘤免疫治疗注入新动力

- “氧化碳”新策略可实现高选择性一氧化碳电解制乙酸

- “量子”《科学》(20231006出版)一周论文导读

- “量子”操控单原子构建新型量子计算平台,可用于研究量子特性

- “反物质”反物质和普通物质都会受引力作用自由下落

- “电荷”预训练通用神经网络CHGNet,实现基于电荷的原子模拟

- “原子”详解2023年诺贝尔物理学奖

- “原子弹”张朝阳模仿“奥本海默”造型 解析电影中原子弹爆炸原理

- “粒子”《奥本海默》中没有她,但物理界不能没有她

- “晶格”我国科学家实现可扩展多体纠缠态的制备和测控

- “原子核”原子核β衰变释放四个粒子模式首次发现