“栅极”揭秘碳化硅芯片的设计和制造

今天,很高兴为大家分享来自电子产品世界的揭秘碳化硅芯片的设计和制造,如果您对揭秘碳化硅芯片的设计和制造感兴趣,请往下看。

众所周知,对于碳化硅MOSFET(SiC MOSFET)来说,高质量的衬底可以从外部购买得到,高质量的外延片也可以从外部购买到,可是这只是具备了获得一个碳化硅器件的良好基础,高性能的碳化硅器件对于器件的设计和制造工艺有着极高的要求,接下来我们来看看安森美(onsemi)在SiC MOSFET器件设计和制造上都获得了哪些进展和成果。

本文引用地址:

Die Layout

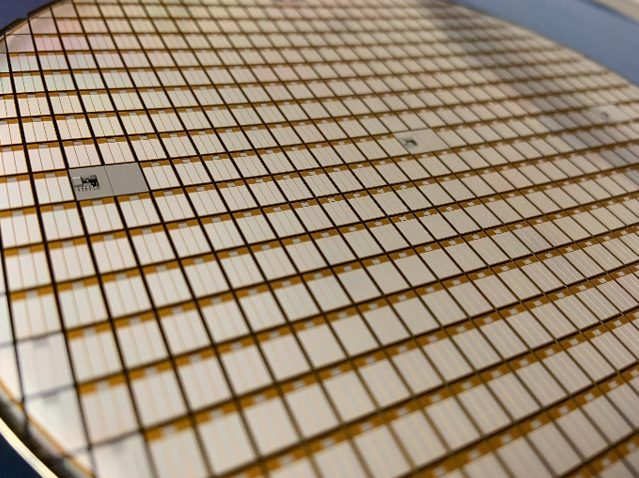

下图是一张制造测试完成了的SiC MOSFET的晶圆(wafer)。

图一

图一芯片的表面一般是如图二所示,由源极焊盘(Source pad),栅极焊盘(Gate Pad), 开尔文源极焊盘(Kelvin Source Pad)构成。有一些只有Gate pad,如上图的芯片就没有Kelvin source pad。

图二

图二在这里我们仔细观察芯片的周围有一个很窄的环形,这个有人叫耐压环,这是很形象的说法。它的作用主要是提升芯片的耐压,我们叫耐压环(Edge termination Ring),通常是JTE结构,其实一个芯片主要就是由三部分构成,Terminal Ring,Gate Pad , Kelvin Source Pad和开关单元(Active Cell),一个芯片外围一圈是耐压环,Gate pad把栅极信号传递到每一个Cell上面,然后里面是上百万个Active Cell。通常大家关注比较多的是Active Cell,因为芯片的开关和导通性能主要是和Active Cell有比较大的关系。在这里我们把芯片的layout还有各个部分的作用特点总结一下,这样方便大家对芯片有一个更好的认识。

▲耐压环(Edge termination Ring)

•环绕着芯片的开关单元,目前大多数采用JTE结构。

•有效控制了漏电流,提高了SiC器件的可靠性和稳定性;

•减小了电场集中效应,提高了SiC器件的击穿电压,SiC MOSFET的击穿电压和具体的每一个开关单元有关,同时和耐压环也有很大的关系。

•防止离子迁移,JTE技术可以用于抑制移动离子的漂移,从而提高SiC MOSFET的可靠性和稳定性。具体来说,JTE技术可以在SiC MOSFET的边缘区域形成一些深度掺杂的控制区域,这些区域可以有效地抑制移动离子的漂移。此外,JTE技术还可以在控制区域中引入一些特殊的物质,例如氮、硼等,这些物质可以与移动离子发生化学反应,从而减少其在MOSFET中的积累和漂移。

▲栅极焊盘和(Gate Pad),开尔文源极(Kelvin Source Pad)

·栅极pad主要作用就一个,把栅极的信号传输到各个开关单元,同时提一下,安森美的芯片是集成了栅极电阻的,这样在模块封装上可以节省空间和一些成本。

·开尔文源极主要是增加了开关速度,减小开关损耗。不过在做并联使用的时候,就需要特别的设计来使用它。

▲开关单元(Active Cell)

·电流导通和关闭的路径

·所有的开关单元是并联

·固定的单元特性下,单元的数量决定了整个芯片的导通电阻大小和短路电流能力。

·目前主要分为平面和沟槽两种结构

我们已经对SiC MOSFET的表面layout有了认识,在SiC的芯片里Edge terminal和Active Cell是非常重要的两部分,安森美在JTE的设计上具有丰富的经验,在SiC MOSET上已经从M1发展到了M3,通过几代的技术迭代发展,JTE设计仿真和制造非常的成熟。我们来总结一下JTE的一些特点和一些设计考虑因素。

SiC JTE(结延伸区)是用于改善硅碳化物(SiC)功率器件电压阻断能力的结构。SiC JTE的设计对于实现所需的击穿电压并避免因器件边缘处高电场而导致的过早击穿至关重要。

以下是SiC JTE设计的一些关键考虑因素:

1. JTE区域的宽度和掺杂:JTE区域的宽度和掺杂浓度确定器件边缘处的电场分布。较宽和重掺JTE区域可以减少电场并提高击穿电压。

2. JTE的锥角和深度:JTE的锥角和深度影响电场分布和击穿电压。较小的锥角和较深的JTE可以减少电场并提高击穿电压。

3. 表面钝化:表面钝化层对于减少表面泄漏并提高击穿电压非常重要。需要特别为SiC JTE器件精心设计和优化钝化层。

4. 热设计:SiC JTE器件可以在比其Si对应物更高的温度下工作。但是,高温也可能降低器件性能和可靠性。因此,在SiC JTE设计过程中应考虑热设计,如散热和热应力。

总体而言,SiC JTE设计是一个复杂的过程,涉及各种设计参数之间的权衡。需要进行仔细的优化和仿真,以实现所需的器件性能和可靠性。

Active Cell 开关单元 – SiC MOSFET的核心

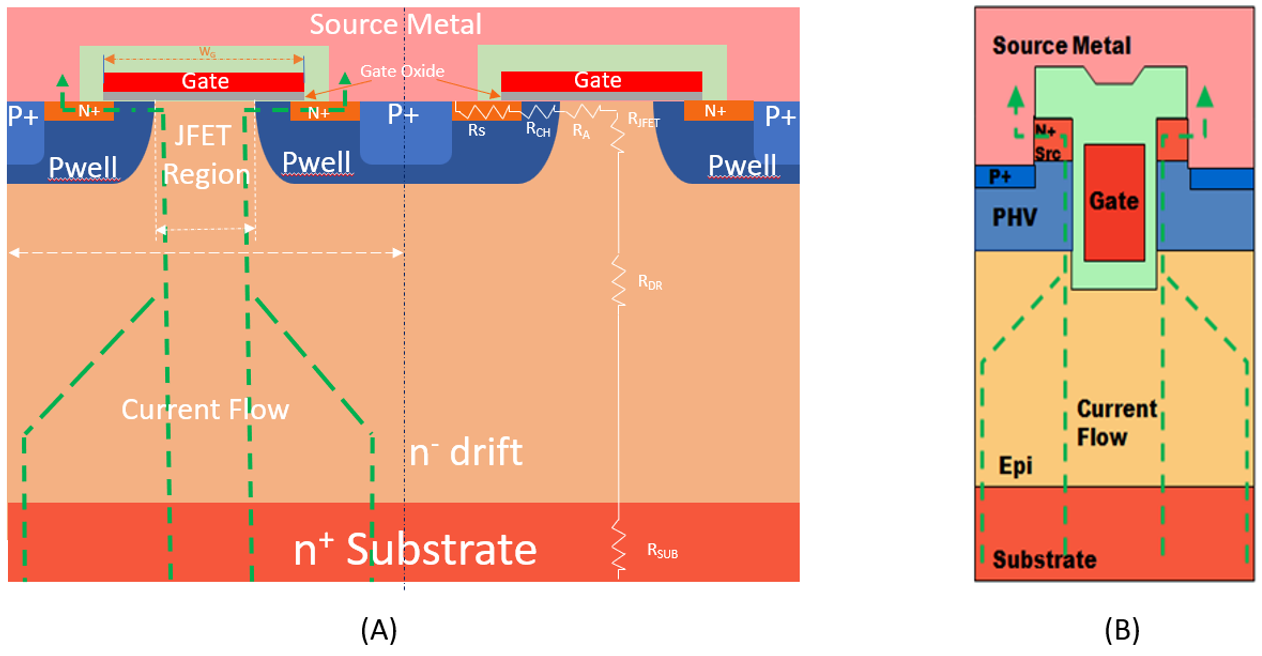

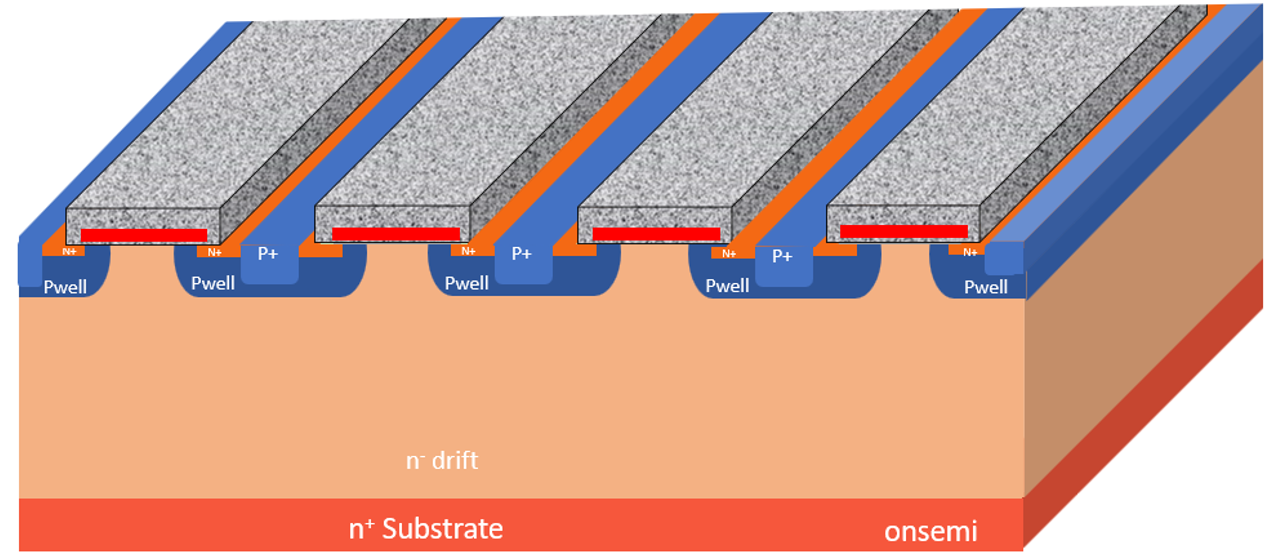

开关单元是SiC MOSFET中一个非常重要的部分。我们可以把MOSFET(硅和碳化硅)根据它们的栅极结构分成两类:平面结构和沟槽结构。它们的示意图如图三所示。如果从结构上来说硅和碳化硅MOSFET是一样的,但是从制造工艺和设计上来说,由于碳化硅材料和硅材料的特性导致它们要考虑的点大部分都不太一样。比如SiC大量使用了干蚀刻(Dry etch),还有高温离子注入工艺,注入的元素也不一样。

图三

图三当前国际上的SiC MOSFET绝大部分都采用了图三A的平面结构,有少部分的厂家采用了图三B的沟槽结构。从发展的角度来看,最终都会衍生到沟槽结构。但是目前的平面结构的潜力还是可以继续深挖的,而沟槽结构也没有表现出它们应当有的水平,在这里我们引入一个统一的尺度来衡量它们的性能 - Rsp(Rdson * area),标识的是单位面积里的导通电阻大小。平面结构的SiC MOSFET具有可靠性高,设计加工简单的优点。安森美用在汽车主驱逆变器里的SiC MOSFET的Rsp 从第一代M1的4.2 mΩ*cm2降低到M2的2.6 mΩ*cm2,目前的最新的M3e常温下的Rsp性能和友商的沟槽结构的SiC MOSFET的水平一致,而高温下的Rsp则低于友商沟槽结构SiC MOSFET的Rsp,达到了行业领先的水平。M3e的cell pitch值和目前的沟槽结构的SiC MOSFET pitch值相当,这表明安森美在平面结构的SiC MOSFET发展优化到了一个相当高的水平。当然一个MOSFET的性能不仅仅看Rsp,还要考虑开关损耗。通过前几代的SiC MOSFET发展,以及根据大量的客户应用反馈,安森美SiC MOSFET器件优化了导通损耗,开通损耗,反向恢复损耗以及短路时间,使得它们在客户的应用中达到最优的一个效率。

SiC MOSFET的平面结构的Active Cell的设计制造方向主要是减小开关单元间距也就是pitch值,提升开关单元的密度,减小Rdson,提升栅极氧化层的可靠性。

如图三A中的结构为了尽可能的减小导通电阻,需要调整开关单元的间距,pitch值和Wg也就是栅极的宽度有一定的关系,pitch值变小,Wg也相应变小,这个对于栅极的可靠性是有一定好处的,在SiC MOSFET里,栅极氧化层(Gate Oxide)非常的薄,小于100纳米,因此在SiC的生产工艺中使用了干式蚀刻的方法来控制加工的精度。

根据图三A中的导通电阻示意图,我们可以得出Rdson=Rs+Rch+Ra+Rjfet+Rdrif+Rsub, 在这里面Rch和Ra占比最大,超过60%以上,所以它们变成了设计和工艺优化的一个重点方向之一。不过也不是一味的减小开关单元栅极的宽度就可以减小Rsp,栅极的Wg宽度减小到一定范围,反而会导致Rsp变大,在设计的时候需要综合考虑以上的参数相互之间的影响,这样才能获得一个比较理想的优化结果,安森美经过几代的工艺迭代发展,其平面结构的SiC MOSFET上已经在性能,良率,可靠性等方面发展得相对成熟。

在芯片里,每个active cell是并联在一起的,图四是一个芯片的截面图的示意图,在这里采用的是带状结构的布局。从这里大家会对于芯片可以有更形象的了解。

图四 芯片的截面图

图四 芯片的截面图以下是SiC MOSFET Rdson设计的一些关键考虑因素:

1. 通道宽度和掺杂:SiC MOSFET的通道宽度和掺杂浓度会影响Rdson和电流密度。较宽和重掺的通道可以降低Rdson并提高电流承载能力。

2. 栅极氧化层厚度:栅极氧化层的厚度影响栅极电容,进而影响开关速度和Rdson。较薄的栅极氧化物可以提高开关速度,但也可能增加栅极漏电流,并增加氧化层击穿失效的风险。

3. 栅极设计:栅极设计影响栅极电阻,进而影响开关速度和Rdson。较低的栅极电阻可以提高开关速度,但也可能增加栅极电容。总体而言,SiC MOSFET Rdson设计是一个复杂的过程,涉及综合考虑各个参数之间的相互影响。需要进行仔细的优化和仿真并且进行试验和测试,以实现所需的器件性能和可靠性。

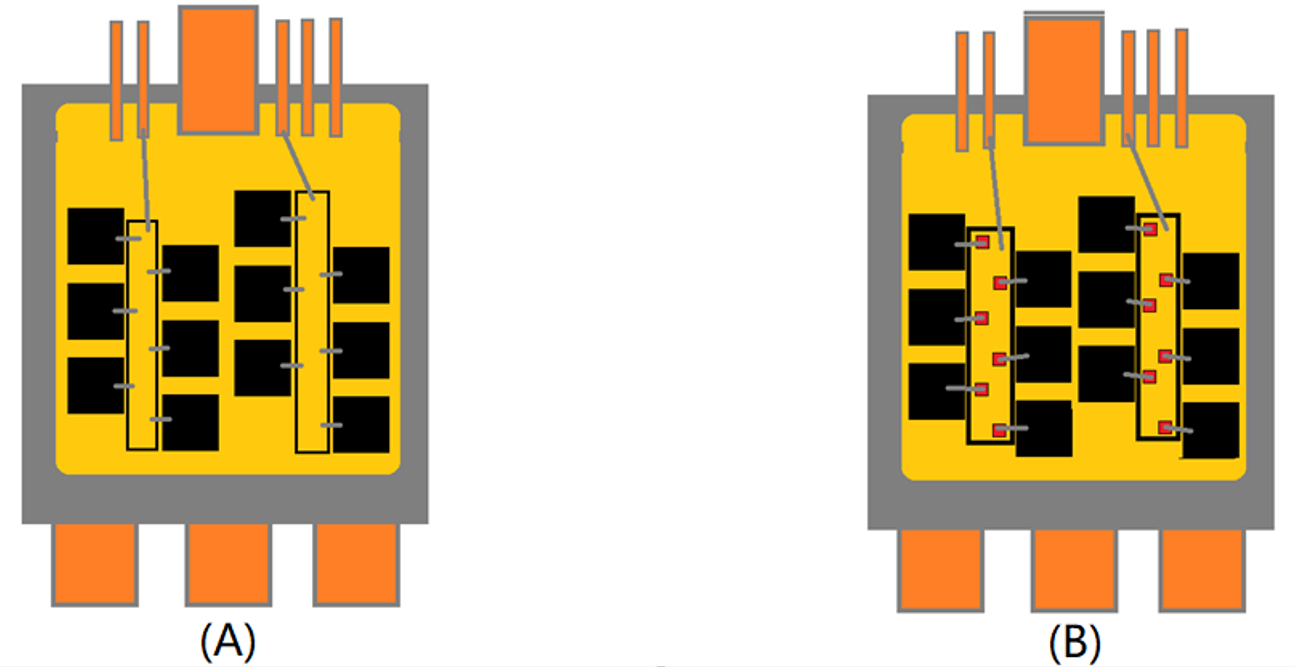

集成片上栅极电阻

安森美所有针对主驱逆变器开发的SiC MOSFET都集成了栅极的电阻,我们可以从图五看到有无电阻的区别。图五A是不需要栅极电阻(芯片上集成了),图五B是需要额外加一个栅极电阻。

图五

图五集成栅极电阻会给模块设计和制造带来一些好处:

•简化了模块绑定线的工艺,降低了失效率。

•减少了焊接电阻到DBC的工艺

•降低了BOM和制造成本

•便于封装的相对小型化设计和制造

由于篇幅关系,加上SiC MOSFET的设计制造工艺非常的复杂,不是三言两语能够阐述的清楚的,希望本文能让大家对SiC MOSFET的设计和制造有一个概念。安森美在SiC 功率器件的设计和制造领域拥有十多年的经验,我们的SiC MOSFET产品经过几代的迭代发展,无论是性能还是品质和可靠性都已经稳定和具有竞争力,非常 欢迎选择和使用我们的SiC MOSFET产品。

好了,关于揭秘碳化硅芯片的设计和制造就讲到这。

版权及免责声明:凡本网所属版权作品,转载时须获得授权并注明来源“科技金融网”,违者本网将保留追究其相关法律责任的权力。凡转载文章,不代表本网观点和立场,如有侵权,请联系我们删除。

相关文章

- “考生”下半年自考即将开始 省考试院发出温馨提示

- “父亲”父亲的眼神杀

- “这是”自内耗到自洽

- “大桥”G3铜陵长江公铁大桥先导索过江

- “某甲”父亲被羁押继母要离婚,未成年女儿谁来抚养?法官多方努力,难题解决了!

- “亚马逊”哪些以色列芯片公司已被美国企业收购?

- “结构”结核杆菌致病机制获揭示

- “装修”装修公司老板明知公司亏损仍吸引客户签合同,骗取上百人700余万,被判11年

- “射电”穿越80亿光年的快速射电暴源于一场“星系交通事故”

- “必胜客”必胜客最黑暗的料理来了

- “结构”结核杆菌致病机制获揭示

- “隐私”Find N3 为用户隐私上锁

- “口信”支持外贸稳规模优结构,金融监管总局发文加强出口信保公司地市级分支结构管理

- “商务部”美对华芯片出口限制“再升级”,商务部:中方对此强烈不满坚决反对

- “小米”雷军官宣全新操作系统 小米将跟MIUI说再见

- “超声波”超声波项目佑航科技获数千万元融资,冲刺明年4000万颗探芯产能|早起看早期

- “芯片”谷歌也打起了小算盘:因自研芯片性能一般,禁止Pixel 8安装测试软件

- “用户”安全芯片+孤岛技术,Find N3成手机安全天花板?

- “云岭”光芯片厂商云岭光电计划IPO

- “标准版”标准版大升级 曝苹果iPhone 16全系标配A18系列芯片